����FPGA�IJ��M늄әC�ŷ�������ͨ��ϵ�y�OӋ

��ϲ������

(�������I��W�Ԅӻ��WԺ������710129)

ժҪ���錍�Fij����C���ŷ��������c��λ�C�Ĵ���ͨ�ţ�����ˑ�����ԓϵ�y�Č��î���

����ͨ�ź�ͬ������ͨ�ŵ�FPGA�OӋ��������B�˒���C���ŷ�����ϵ�y�Ę��ɣ�Ԕ���ˮ���

����ͨ�Ÿ�������ģ�K����늾��a���}�_Ӌ��ֵͬ�����аl�͵���λ�C��FPGA�OӋ�c���挍

�F�������C��ԓ�OӋ�r�����_�����F�˹���ָ�ˣ��_�����ŷ��������c��λ�C��ͨ�š�

�P�I�~��FPGA����������ͨ�ţ�ͬ������ͨ�ţ��ŷ�����ϵ�y�����M늄әC

O �� ��

���M늙C�ŷ��������ǒ���C���ĺ��ģ���ͨ��ϵ�y���ŷ����������P�I����ϵ�y���û�����������늾��a���ɼ����M늙C���ٶȺͽǶ���Ϣ���ŷ����������y���OӋ���������Æ�Ƭ�C��DsP����λ�C�M��ͨ�š����IJ���FPGA������λ�C������Ӳ�������Z��Verilog HDL���OӋ�˒���C���ŷ�������ͨ��ϵ�y��FPGA����ֲ�ԏ���ֻ��Ҫ���ε���Ӳ���ӿںʹ���ͨ�Ÿ�ʽ���Ɍ��FFPGA�Ͳ�ͬ����λ�C�ĸ��ٴ���ͨ�š�

l�ŷ�����ϵ�y����

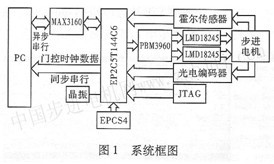

ij����C��ϵ�y��D��Dl��ʾ����ϵ�y�����]�h���Ʒ�ʽ�Ӳ��M늙C��׃�ٵ��B�m�A�ܒ��裬���Ӓ���C�����F���_���趨λ��

������ͬ�r�̵��ٶȣ���FPGA�OӋ�ļ�����ģ�K(EP2c5T144c6)�a����ͬ�l�ʵ��}�_�����}�_����ݔ���惦��FPGA�ȵļ��֔�����������оƬ�������֔����M�Дز����Ʋ��M늙C�D�ӣ��Ķ����ƒ���C�������A����ʽ�D����1�������������������ŷ�������λ�û��ʣ�ݔ������̖�c��늾��a������λ��̖���_���Cе���c������оƬ�x��EPcS4����늺���늕r��FPGA�M�����á�

FPGA����늾��a��ݔ�����}�_��̖�M��4����Ӌ��������Ҫ��ͨ�^ͬ�����ڰl�ͽoPc�C��FPGA�ڽ��յ�Pc�Cָ���ͨ�^�������ڷ����b�y��������Pc�C�������صĔ�������늾��a��Ӌ��ֵ��ͨ�^����������FPGA�l��ָ������Ʋ��M늙C��

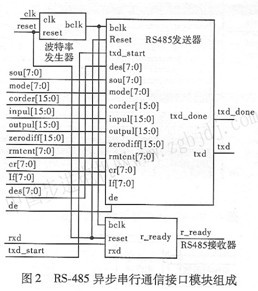

��ϵ�y�Ю�������ͨ�ŵ������ӿڞ�RS485�����p�����đ���ʽ�������ʞ�9 600 bps������Verilog�Z�Ծ���������ɔ����Ľ����c�l�͡��ƽ�D�Q����MA��M��˾���a��MAX3160���@��һ������ܵĶ��f�h�հl�������ɾ��̿��ư��p����ȫ�p��Rsһ485��422��RS232ģʽ��

2 FPGA��������ͨ��ģ�K

��������ͨ��ģ�K��FPGAоƬ�Ȳ���Ӳ��߉�OӋ���������ʰl������Rsһ485��������Rsһ485�l������3-5������D2��ʾ��

2��1�����ʰl����

�����ʰl�����a���ķ��l�r犣����Dz����ʕr犣����Dz����ʕr��l�ʵ�16������ݔ��rxd�����M�вɘӣ����ֽ������cPc�Cͬ����Ŀ���Ǟ����ڽ��Օr�M�о��_�زɘӣ�����ȡ�����Ĵ��Д����������ʰl���������o����ϵ�y�r��l�ʺ�Ҫ��IJ�����Ӌ��������ʷ��l���ӣ�������IJ����ʷ��l����������l���ķ��l����Ӌ�㹫ʽ�飺���l��=ȫ�֕r犣�(16������������)һ1��

2��2 Rs-485������

RSһ485����������Pc�C�l�͵�ָ��������D���鲢�Д�����FPGA���Ɔ�Ԫ�����˔��������Ʋ��M늙C���D�ӡ�Pc�C�l����̖�ַ���ʽ�飺1λ��ʼλ��8λ����λ��1λ�ɳ̿�λ(���R��ַ��)��1λֹͣλ��

���ڴ��Д������ͽ��Օr��Ǯ����ģ���߉l�D����߉O���Ա�ҕ��һ������������ʼλ�����˱���ë��Ӱ푣���Ҫ����4���B�mbclk��߉O�����յ������J����ʼλ���յ���

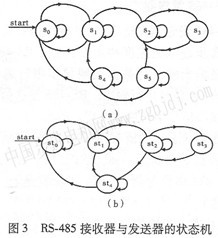

Rs.485�������Ľ��ՠ�B�C���̈D��D3(a)��ʾ����B�Cһ����6����B��sO(�ȴ���ʼλ)��s1(���λ�����c)��s2(�ȴ��ɘӔ���λ�ͳ̿�λ)��s3(����λ�ɘ�)��s4(�̿�λ�ɘ�)��s5(�惦������ֹͣλ����)��

sO��B��������������λ���ՠ�B�C��̎���@һ��B��һ���_����ʼλ��������B�C���D��sl��B���D4(a)�е�rxd��syne O����d��syncl��rxd��sync��̖��rxd��ͬ����̖�������ų��ɔ_��̖���z�y���^ͬ�����rxd��sync��̖��

s1��B�����ڮ���������̖����ÿλ�����c�z�yλ��̖���ܱ��C���^��Ĕ���λ�z�y�ĕr��Ӌ�`���^С���ڱ���B����������ʼ |