���ڏ�(f��)�s�ɾ���߉�����Ķಽ�M(j��n)늙C(j��)�֕r(sh��)����

ʯ�Ʒ壬�ο��A

(�Ї��ƌW(xu��)Ժ������W(xu��)���ܙC(j��)е�о������������710119)

ժҪ������(j��)��I��0�ڵ����c(di��n)���O(sh��)Ӌ(j��)�����\(y��n)��(d��ng)���ƿ��Ŀ���F���ڏ�(f��)�s�ɾ���߉����(CPLD)�Ķಽ�M(j��n)늙C(j��)���ơ����\(y��n)��(d��ng)���ƿ�ϵ�y(t��ng)����λ�C(j��)��ͨ�^��CPLD�����M(j��n)��늙C(j��)�ķ֕r(sh��)���ơ������\(y��n)��(d��ng)���ƿ���ݔ�롢ݔ�������ù�����x����˿��ɔ_������(qi��ng)���}�_ݔ���l���`���ʵͣ�ͬ�r(sh��)��CPLD���и������ܣ����_(d��)���ж��_���M(j��n)늙C(j��)���ٶȼ�λ�õľ��_���ơ�

�P(gu��n)�I�~���\(y��n)��(d��ng)���ƿ������M(j��n)늙C(j��)����(f��)�s�ɾ���߉��������

�ЈD���̖��TM 383 6�īI(xi��n)��(bi��o)־�a��A���¾�̖��16734540(2010)064)0354)3l

0 ����

���M(j��n)늙C(j��)�ڹ��I(y��)��������I(l��ng)��đ�(y��ng)�÷���Խ��Խ�V����ͬ�đ�(y��ng)��Ҫ��ͭh(hu��n)����늙C(j��)�Ŀ���Ҳ����˲�ͬ���O(sh��)Ӌ(j��)���������^��Ҋ��ᘌ���(sh��)�F(xi��n)�ಽ�M(j��n)늙C(j��)�Ŀ����ЃɷN��(1)��ȫ�����\(y��n)��(d��ng)���ƿ���ԓ�����O(sh��)Ӌ(j��)���Σ�����Ҫ����(g��)�\(y��n)��(d��ng)���ƿ�����Ӳ�����B����Ҳ���^��(f��)�s��(2)ͨ�^�\(y��n)��(d��ng)���ƿ�+�^���������늙C(j��)�Ŀ�����Ҫ����(g��)�^���ռ�ÿ��g�����M(f��i)�ɱ������Ľ�B��ϵ�y(t��ng)�����\(y��n)��(d��ng)���ƿ�������λ�C(j��)����늙C(j��)�M(j��n)�зֽM�x��(f��)�s�ɾ���߉����(Complex Programmable Logic Device��CPLD)������λ�C(j��)����늙C(j��)��ͨ�࣬������·������(ji��)�s�˳ɱ���

1 ϵ�y(t��ng)���w�Y(ji��)��(g��u)

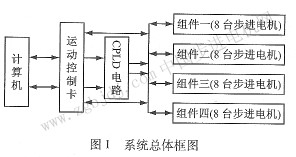

ԓϵ�y(t��ng)���\(y��n)��(d��ng)���ƿ�ģ�K��CPLD�·��4��(g��)�M������ģ�K(ÿ�M��8�_����32�_늙C(j��))�ȽM�ɡ����M������ģ�K���(d��)�����քe���ڿ��Ƹ��M����늙C(j��)�\(y��n)��(d��ng)�����Ʋ��ֲ������ڱ��锵(sh��)�ؼ��g(sh��)����˾��ADT8940�\(y��n)��(d��ng)���ƿ���Xilinx��˾��XC9536CPLD������Ҫ����32�_늙C(j��)�����˜p�ٔU(ku��)չI��O�ڵ��O(sh��)Ӌ(j��)��ϵ�y(t��ng)����CPLDȡ�����y(t��ng)�Ć�Ƭ�C(j��)[1]���\(y��n)��(d��ng)���ƿ�ͨ�^PCI�����cӋ(j��)��C(j��)ͨ�ţ���ɂ�(g��)�_�P(gu��n)����ݔ����̖����CPLD��ݔ_����̖���M(j��n)��늙C(j��)�ķֽM�x��CPLD��ݔ����̖ͨ�^ģ�M�_�P(gu��n)74HC4052ʹ���x�нM��늙C(j��)��(d��o)ͨ��ϵ�y(t��ng)���w�Y(ji��)��(g��u)��D1��ʾ��

2ϵ�y(t��ng)��Ӳ���O(sh��)Ӌ(j��)

2��1�\(y��n)��(d��ng)���ƿ�ģ�K

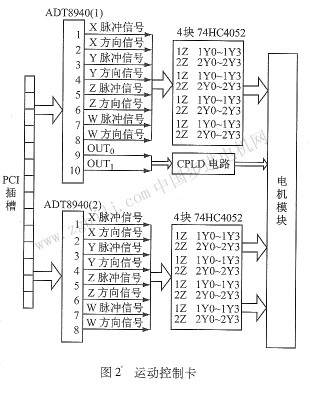

�\(y��n)��(d��ng)���ƿ����늙C(j��)�\(y��n)��(d��ng)���Ƶ����м�(x��)��(ji��)�������}�_�ͷ�����̖��ݔ�����Ӝp�ٵ�̎����ԭ�c(di��n)����λ��늙C(j��)�ķֽM�x����̖�ȡ��\(y��n)��(d��ng)���ƿ�����(j��)Pc�C(j��)�Č�(sh��)�r(sh��)����ָ�����M(j��n)늙C(j��)�(q��)��(d��ng)���l(f��)���}�_������ȿ�����̖��ͨ�^����(y��ng)�IJ��M(j��n)늙C(j��)�(q��)��(d��ng)���(q��)��(d��ng)늙C(j��)�\(y��n)�С�ϵ�y(t��ng)���õ�ADT8940���������c(di��n)[2]��(1)����PCI�����ĸ������ŷ������M(j��n)

���ƿ���֧�ּ��弴�á�(2)�}�_ݔ����ʽ���Æ��}�_(�}�_+����)���p�}�_(�}�_+�}�_)��ʽ��ԓϵ�y(t��ng)���Æ��}�_��ʽ��****�}�_�l��2 MHz���������M(j��n)���g(sh��)�����C��ݔ���l���^�ߕr(sh��)���l���`��С��0��1����(3)�ٶȿ��ƿ��ö��ٺ����μӜp�١���(4)λ�ù������Ãɂ�(g��)�ӣ��pӋ(j��)��(sh��)����һ��(g��)���ڃ�(n��i)�������(q��)��(d��ng)�}�_ݔ����߉λ��Ӌ(j��)��(sh��)����һ��(g��)���ڽ����ⲿ��ݔ�룬ݔ����̖��A��B��ݔ��ľ��a�����ųߣ����錍(sh��)�Hλ��Ӌ(j��)��(sh��)����(5)֭��(sh��)��λ��(sh��)���_(d��)32λ��****������һ2 147 483 648��+2 147 483 647��(6)�����롢ݔ�������ù�����x�����ɔ_�ԏ�(qi��ng)���\(y��n)��(d��ng)����Rģ�K���P(gu��n)�I����ܛ���O(sh��)Ӌ(j��)����Ҫ�Ǹ���(j��)Pc�C(j��)�Č�(sh��)�r(sh��)ָ��Ƀɂ�(g��)�_�P(gu��n)ݔ����0uL��OuT������cPLD��ݔ����̖�M(j��n)��늙C(j��)�ֽM�x���}�_�ͷ�����̖�քe�ӵ�8�Kģ�M�_�P(gu��n)74Hc4052��16��(g��)�����ˣ��ɷֽM��̖�xͨ�����늙C(j��)������ADT8940�����S���ƿ�����ϵ�y(t��ng)ÿ��(g��)�M����8�_늙C(j��)��������Ҫ2���\(y��n)��(d��ng)���ƿ�����D2��ʾ��

2��2 CPLD�·

����(g��)ϵ�y(t��ng)�����_�M������Ҫ��ͬһ�r(sh��)�gֻ��һ�_�M���ڹ����������Ƿ֕r(sh��)�����ģ���˿���ͨ�^cPLD�����·���x���Ă�(g��)�е�һ��(g��)�M���������Ҫ�{(di��o)�������M���������ٴ��M(j��n)���x��ϵ�y(t��ng)����xilinx��˾��xc9536cPLD����x00500ϵ����������һ������ܡ������c(di��n)�Ŀɾ���߉�������ĽY(ji��)��(g��u)�Ͽ������������(g��)��Ԫ�����Ԫ���ɾ���I��O��Ԫ�Ϳɾ��̵ă�(n��i)���B��������Ҫ���c(di��n)���£�(1)�����ܡ������пɾ������_֮�gpin��pin�ӕr(sh��)5 ns��ϵ�y(t��ng)�ĕr(sh��)��ٶȿ��_(d��)��i00 MHz��(2)��������������������36��(g��)���Ԫ������ϵ�y(t��ng)�T��800��(g��)��(3)5 V��ϵ�y(t��ng)���̣����Ծ���lO000�Ρ�(4)���Џ�(qi��ng)��ď�(qi��ng)�_�i��������(5)ÿ��(g��)���Ԫ���пɾ��̵���ģʽ��(6)�]���õ����_�о��̽ӵ�������

����cPLD�·���\(y��n)��(d��ng)���ƿ��ăɂ�(g��)�_�P(gu��n)��ݔ����̖����cPLD�� |